1.AXI기본개념

AXI의 기본개념입니다

솔직히 말해서 처음공부할때 와닿지 않았습니다.

즉 통신이름중 하나라고 생각하면 편할거 같습니다

AXI의 기본은 DATA를 제공해주는 Source(Master)

DATA를 받는 Destination(Slave)로 구성되어있습니다

Source(Master)에서는 VALID 신호를 제공하고 Destination(Slave)에서는 READY신호를 제공합니다

즉 데이터가 엉키지 않도록 Master에서는 Valid신호를 줌으로써 데이터 전송준비완료 신호를 주는것이고, 그와함께 전송할 Data도 전송합니다

Slave에서는 Data를 받을 준비가 되었다면 READY 신호를 줌으로써 Data를 전송받게 됩니다

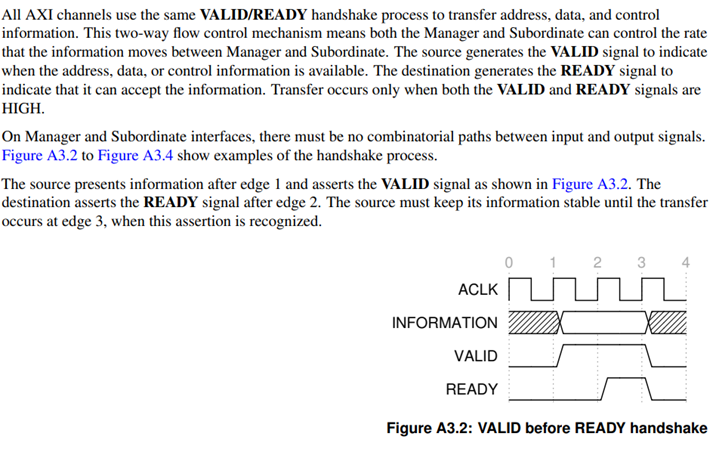

Timing Diagram

이와같이 VALID READY 신호가 동시에 HIGH여야 DATA가 전송되는 것입니다

AXI에서는 총 5개의 Channel을 통해 통신을 하게 됩니다

Read Operation일때는 Slave에서 Address를 받으면 해당 주소의 Data를 전송하면 되니, Response는 필요없게 되겠지요.

각 5개의 Channel

Read Address

Read Data

Write Address

Write Data

Write Response Channel 모두 Valid, Ready 신호를 갖고있습니다

따라서 이와같이 Timing도를 만들게 됩니다, 빨간색 박스 쳐져있는 부분일때 Data가 전송되겠죠

이를 HandShake라고 합니다

2.코드리뷰

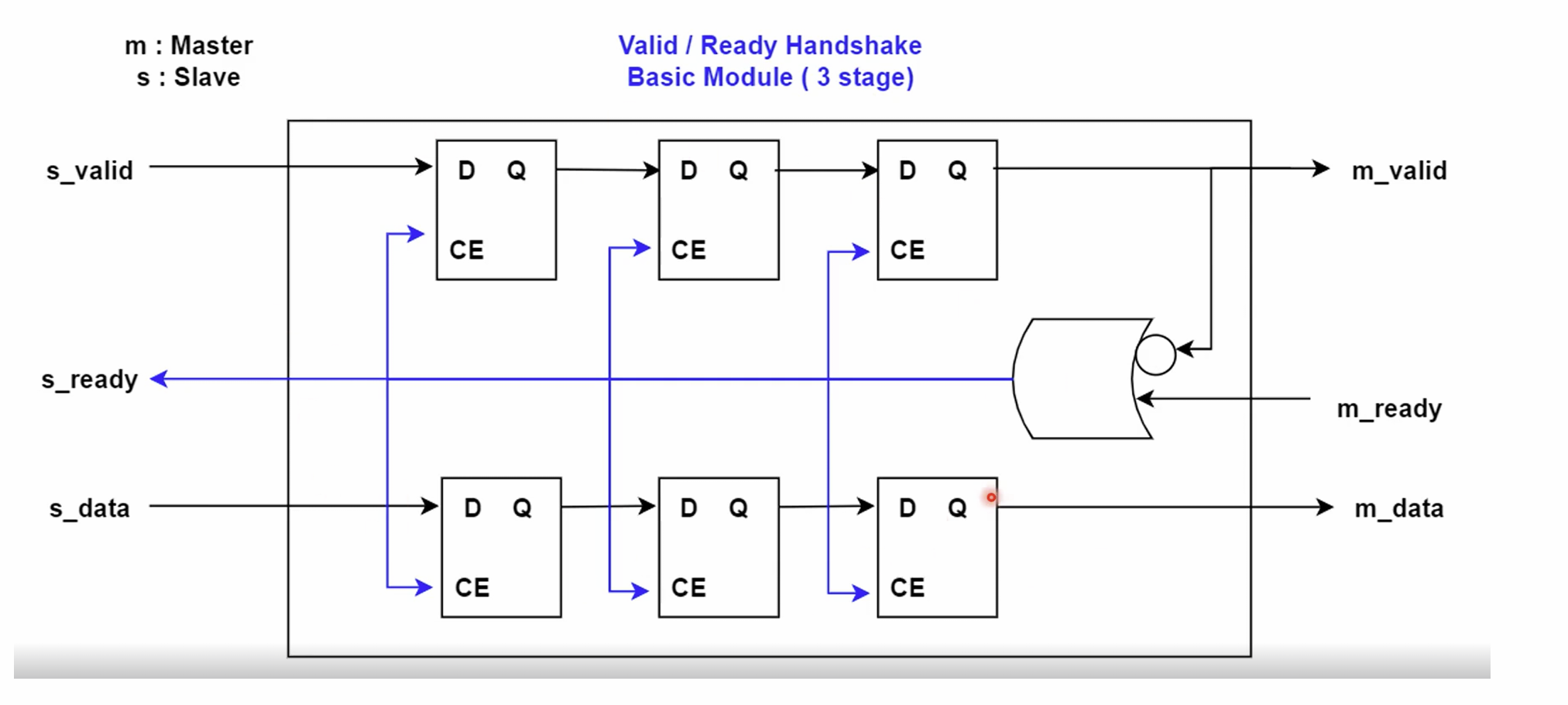

기존 아키텍쳐이다.

앞에있는 Slave 에서 S_valid 신호가 on 되면 D F/F에 Data가 들어가게 된다.

1. D F/F에 Data가 없는상태라면 Q=0이므로 D F/F안에 Data가 들어가도 되는 상태이다.

따라서 Inverter를 씌워 s_ready를 출력하도록한다. 그렇게되면 s_data가 m_data로 출력되게 된다

2. D F/F에 Data가 있는 상태라면 Q=1이므로 s_ready신호는 m_ready 신호에따라 출력값이 변화하게된다

즉 m_ready, 뒤에있는 Master Slave Module에서 ready신호가 들어와야 Data가 전송되는것이다

이 사진은 자신의 곱이 power2로, 자신의 제곱의 곱이 power4로, power4의 제곱이 power8로, 즉 자기 자신의 8승을 계산하는 모듈이다.

위 사진을 보게되면 D F/F에 자신의 곱을 곱해서 저장하는 Flow라고 생각하면 된다

또한 valid 신호에 맞게 data가 흘러가도록 설계를 해야한다

왼쪽 코드를 보면 큰 Box의 input output을 설정해주었고

s_value는 32bit로 설정

그의 곱이되니, 2^32 * 2^32 =2^64이므로

output은 64bit로 설정해 줘야한다

reg로 설정된 r_power_of_2,4,8은 D F/F에 해당한다

wire로 설정된 power_of_2는 D F/F에서 출력된 값을 다음 D F/F에 연결하기 위해 사용해주어야 한다

assign s_ready = ~m_valid | m_ready; //이 코드는 위 그림에서 OR 연산자 쪽을 나타내주는 쪽이다

else if (s_ready)

begin

r_valid <= {r_valid[1:0], s_valid}; //이쪽부분은 s_valid가 들어왔다면

end //Data가 다음 F/F으로 넘어갈수

있도록 해야하기 때문에, 이와같이 설계해 주었다

s_ready가 on이 되면 wire에 있던 data가 F/F안에 저장되어야 한다

assign문은 제곱하는 논리를 써놓은것이다

r_valid는 3개의 F/F에 들어가기때문에 [2:0]r_valid로 설정되어있다.

그중 r_valid[2] 는 m_valid에 해당하므로 assign문을 구성해주고

m_power_of_8은 뒤에있는 Master 단으로 들어가는 data기 떄문에 r_power_of _8을 연결해주었다

이렇게 testbench 출력결과가 나오게됩니다

input data측에서 3번의 hand shake가 발생했으므로 1 ,2 3 의 data가 들어가게되고

이후 output 에서 2번의 hand shake가 발생해 1의 8승인 1, 2의 8승인 256이 출력되게 됩니다.

'AXI' 카테고리의 다른 글

| [AXI]AXI4 Standard (0) | 2025.02.04 |

|---|---|

| [AXI]AXI Lite 실습 (1) | 2025.01.16 |

| [AXI]AXI4-Stream (1) | 2025.01.15 |

| [AXI] AXI4-Lite Interface (1) | 2025.01.14 |

| [AXI]2.FIFO (0) | 2025.01.06 |