[AXI]RDMA 이론

DMA는 Direct Memory Access의 약자이다

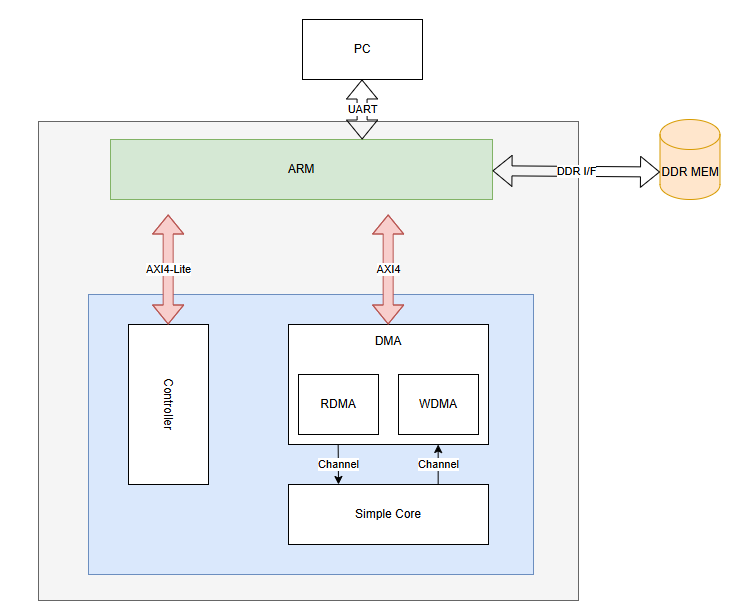

DMA IP를 설계하면 HardWare가 직접 외부에 있는 메모리의 Data를 Read와 Write를 할 수 있게된다.

DDR Controller가 DDR Interface로 접근하여 외부에 있는 메모리에 Data를 적게되는것이다

DRAM에 접근하기 될때 중요한 Performance 요소가있다

1. DATA BIT WIDTH(BUS WIDTH)

2. Pipline

1.Multiple Outstanding address

2.Burst Length

3.Acces pattern

1.Random Access vs Incremental Access

1. DATA BIT WIDTH(BUS WIDTH)

Ideal Bandwidth = (Byte/cycle)*Frequency

8byte*100MHz= 800Mbytes/s

한 사이클에 Access할수있는 Bit의 수이다. 즉 이 값이 클수록 많은 data를 가져올 수 있다는 것이다

Zybo Z7 Board의 Data sheet를 보게되면 1066Mbps를 데이터속도로 지원하고 최고 전송속도는 8533Mbit/s라고한다

이를 Byte로 환산 1066이게된다

2. Pipline

1.Multiple Outstanding address

2.Burst Length

위 두 사진을 보게되면 Pipeline이 적용되는것을 볼 수 있다.

Multiple Outstanding Address를 사용하게되면, AW에서 A라는 주소에 대한 동작을 할때 본래 Response 신호를 받고 다음 주소 B를 받는것이 정석적이지면 B라는 주소를 미리 받아놓으면 Pipeline동작을 할 수 있어 이점이 있다

또한 Burst Length를 사용하게되면 지속적으로 Data를 쭉 불러올수 있으므로 이점이 있다

3.Acces pattern

DRAM은 이와같이 1T1C구조로 이루어져있다

커패시터에 전기에 충전이 되면 논리 '1' ,전기에 충전이 안되어있다면 논리 '0'이게된다

Row와 Column에 전압을 줘서 해당 Cell의 전압의 충방전을 하게된다

이와같이 빨간색의 4개의 Cell에 Data를 적는경우와 파란색의 4개의 Cell에 Data를 적는경우를 생각해보자

이런식으로 Cell에 접근하게된다

RAS와 CAS는 Row Address Strobe, Column Address Strobe의 약자이다

빨간색의경우는 RAS를 Active시켜 계속 유지시키고 CAS만 변화시키면되고

파란색의 경우는 RAS와 CAS를 계속 변화시켜줘야한다 따라서 빨간색으로 Cell에 접근하게되면 효율성이 있다는것이다

이와같이 DMA가 동작하게 되는것이다

RDMA에 대해서 AXI4-Standard를사용하게되므로 그에 대해서 설명하게되면

이와같이 AXI4-Lite state를 구성해줬었는데 이렇게되면 Multiple Out standing addRess사용이 불가능해진다

RDIDLE이 되어 ARVALID가 들어오게되면 RDDATA가 되고 RDDATA가 됐을때 RREADY&RVALID가 들어오게되면 다시 RDIDLE이 되게된다

AR Channel과 R Channel의 종속성이 있어 MOR를 사용하지못한다

따라서 두 채널이 무관하게 동작할수있도록 해야한다

이렇게 바뀌어야하고

AR을 먼저 FIFO에 받아놓고 put 되고 RDATA가 끝날때 바로 FIFO에서 get하여 pipeline을 하게 되는것이다

FSM도 바뀌어야하는데

RDMA는 run이라면 S_PRE에서 S_RUN이되고 모든 DATA를 읽어왔다면 S_DONE이된다

S_PRE STATE는 DATA를 가져올때 DATA준비 과정을 기다리기 위해 넣었다 1Cycle을 기다려주기위해

AR FSM은

FIFO가 FULL이 아니고 마지막 request가 아니고 즉 가장 마지막 데이터가 아니면 S_PRE가 되게되고,

S_RUN에서 AR_HANDSHAKE가 되면 다시 S_IDLE이 된다

R FSM은 FIFO가 비어있지않다면 SRUN이 되고 fifo가 비어있고 burst_done이 됐다면 S_IDLE이 된다